## **Instruction Manual**

## **Tektronix**

DAS 92DM911 Futurebus+ Bus Support 070–8747–00

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to the Safety Summary prior to performing service.

Please check for change information at the rear of this manual.

First Printing: February 1993

#### **Instrument Serial Numbers**

Each instrument manufactured by Tektronix has a serial number on a panel insert or tag, or stamped on the chassis. The first letter in the serial number designates the country of manufacture. The last five digits of the serial number are assigned sequentially and are unique to each instrument. Those manufactured in the United States have six unique digits. The country of manufacture is identified as follows:

| B010000 | Tektronix, Inc., Beaverton, Oregon, USA |

|---------|-----------------------------------------|

| E200000 | Tektronix United Kingdom, Ltd., London  |

| 1000000 | Canal/Taldwards Janan                   |

J300000 Sony/Tektronix, Japan

H700000 Tektronix Holland, NV, Heerenveen, The Netherlands

Instruments manufactured for Tektronix by external vendors outside the United States are assigned a two digit alpha code to identify the country of manufacture (e.g., JP for Japan, HK for Hong Kong, IL for Israel, etc.).

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077

Printed in U.S.A.

Copyright © Tektronix, Inc., 1993. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. The following are registered trademarks: TEKTRONIX, TEK, TEKPROBE, SCOPE-MOBILE, DAS, PRISM, TekDB, KlipChip, and FasTrak.

#### WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Tektronix will provide such service at Customer's site without charge during the warranty period, if the service is performed within the normal on-site service area. Tektronix will provide on-site service outside the normal on-site service area only upon prior agreement and subject to payment of all travel expenses by Customer. When or where on-site service is not available, Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

#### **SOFTWARE WARRANTY**

Tektronix warrants that the media on which this software product is furnished and the encoding of the programs on the media will be free from defects in materials and workmanship for a period of three (3) months from date of shipment. If any such medium or encoding proves defective during the warranty period, Tektronix will provide a replacement in exchange for the defective medium. Except as to the media on which this software product is furnished, this software product is provided "as is" without warranty of any kind, either express or implied. Tektronix does not warrant that the functions contained in this software product will meet Customer's requirements or that the operation of the programs will be uninterrupted or error-free.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period. If Tektronix is unable to provide a replacement that is free from defects in materials and workmanship within a reasonable time thereafter, Customer may terminate the license for this software product and return this software product and any associated materials for credit or refund.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPLACE DEFECTIVE MEDIA OR REFUND CUSTOMER'S PAYMENT IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

## **Table of Contents**

| Preface:   | GUIDE TO DAS 9200 DOCUMENTATION GENERAL SAFETY SUMMARY/ DISASSEMBLERS | vi           |

|------------|-----------------------------------------------------------------------|--------------|

| Section 1: | OVERVIEW                                                              |              |

| Section 1. | DAS 9200 SYSTEM SOFTWARE COMPATIBILITY                                | 1-2          |

|            | DAS 9200 CONFIGURATION                                                | 1-2          |

|            | ABOUT THIS MANUAL                                                     | 1-3          |

|            | Manual Conventions                                                    | 1-4          |

| Section 2: | INSTALLATION AND CONNECTIONS                                          |              |

|            | CONFIGURING THE DAS 9200                                              | 2-1          |

|            | INSTALLING SOFTWARE                                                   | 2-3          |

|            | CONNECTING TO THE SYSTEM UNDER TEST                                   | 2-4          |

|            | CONFIGURING THE PROBE ADAPTER                                         | 2-6          |

|            | Sync/Async Switches                                                   | 2-7          |

|            | Glitch Filter Delay Switch                                            | 2-8          |

|            | Data Path Width Switch                                                | 2-8          |

|            | Jumpers                                                               | 2-8          |

|            | LED INDICATORS                                                        | 2-9          |

| Section 3: | SETTING UP DISASSEMBLER SOFTWARE                                      |              |

|            | MODULE SUPPORT AND SUPPLIED SETUPS                                    | 3-2          |

|            | Full Main Bus and Arb Bus Supplied Setup                              | 3-3          |

|            | Partial Main Bus and Arb Bus Supplied Setup                           | 3-3          |

|            | Full Main Bus Only Support                                            | 3-3          |

|            | Partial Main Bus Only Support                                         | 3-3          |

|            | Arb Bus Only Supplied Setup                                           | 3-3          |

|            | LOADING SUPPORT SOFTWARE                                              | 3-4          |

|            | RESTORING SUPPLIED SETUPS                                             | 3-4          |

|            | CREATING MULTIMODULE SETUPS                                           | 3-5          |

|            | CHANNEL GROUPS AND ASSIGNMENTS                                        | 3-6          |

|            | CHANGES THAT AFFECT DISASSEMBLY                                       | 3-6          |

|            | CLOCKING                                                              | 3-6          |

|            | Main Bus                                                              | 3-7          |

|            | Arb Bus                                                               | 3-8          |

|            | SYMBOLS                                                               | 3-8          |

|            | TRIGGERING                                                            | 3-18         |

|            |                                                                       | 5 10         |

| Section 4: | ACQUIRING AND VIEWING DISASSEMBLED DATA ACQUIRING DATA                | 4-1          |

|            | VIEWING DISASSEMBLED MAIN BUS DATA                                    | 4-1          |

|            |                                                                       | 4-12         |

|            | Error Reporting                                                       |              |

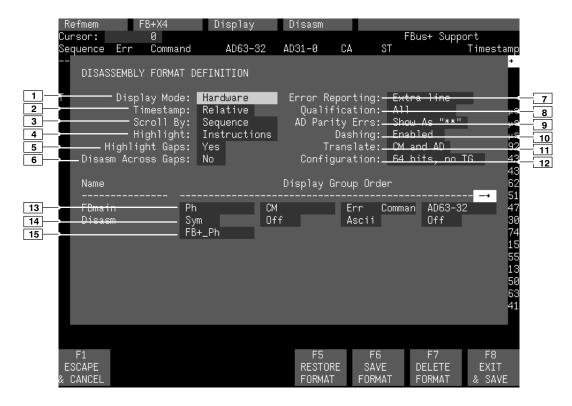

|            | Disassembly Format Definition Overlay                                 | 4-12         |

|            | Displaying Off-Screen Channel Groups                                  | 4-17         |

|            | Displaying Channel Groups Symbolically                                | 4-18         |

|            | SEARCHING THROUGH DATA                                                | 4-18         |

|            | PRINTING DATA                                                         | 4-19<br>4-20 |

|            | REFERENCE MEMORY                                                      | 4-70         |

| Section 5:         | GENERAL PURPOSE ANALYSIS                                                    |           |

|--------------------|-----------------------------------------------------------------------------|-----------|

|                    | CLOCKING                                                                    | 5-1       |

|                    | Custom Clocking                                                             | 5-2       |

|                    | Internal Clocking                                                           | 5-2       |

|                    | External Clocking                                                           | 5-2       |

|                    | TRIGGERING                                                                  | 5-3       |

|                    | ACQUIRING DATA                                                              | 5-3       |

|                    | DISPLAYING DATA                                                             | 5-3       |

|                    | Timing Menu                                                                 | 5-3       |

|                    | State Menu                                                                  | 5-5       |

|                    | SEARCHING THROUGH DATA                                                      | 5-5       |

|                    | PRINTING DATA                                                               | 5-6       |

| Annendix A.        | ERROR MESSAGES AND DISASSEMBLY PROBLEM                                      | S         |

| rippendix 11.      | MODULE ERROR MESSAGES                                                       | .S<br>A-1 |

|                    | OTHER DISASSEMBLY PROBLEMS                                                  | A-3       |

|                    | OTTLER DISTIBLE TROBLEMS                                                    | 71.5      |

| <b>Appendix B:</b> | HOW DATA IS ACQUIRED                                                        |           |

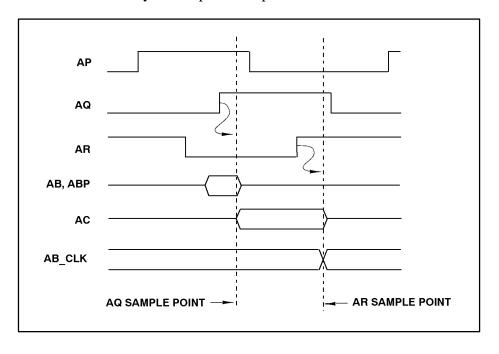

|                    | CLOCKING FOR THE MAIN BUS                                                   | B-1       |

|                    | Custom Clocking                                                             | B-2       |

|                    | CLOCKING FOR THE ARB BUS                                                    | B-3       |

| Appendix C:        | SERVICE INFORMATION                                                         |           |

| iippenam et        | SERVICE SAFETY INFORMATION                                                  | C-1       |

|                    | PROBE ADAPTER DESCRIPTION                                                   | C-1       |

|                    | CONFIGURING THE PROBE ADAPTER                                               | C-2       |

|                    | Sync/Async Switches                                                         | C-3       |

|                    | Glitch Filter Delay Switch                                                  | C-4       |

|                    | Data Path Width Switch                                                      | C-4       |

|                    | Jumpers                                                                     | C-5       |

|                    | LED INDICATORS                                                              | C-6       |

|                    | CARE AND MAINTENANCE                                                        | C-7       |

|                    | CHANNEL ASSIGNMENTS                                                         | C-8       |

|                    | DISCONNECTING PROBES                                                        | C-18      |

|                    | REMOVING AND REPLACING PODLETS                                              | C-19      |

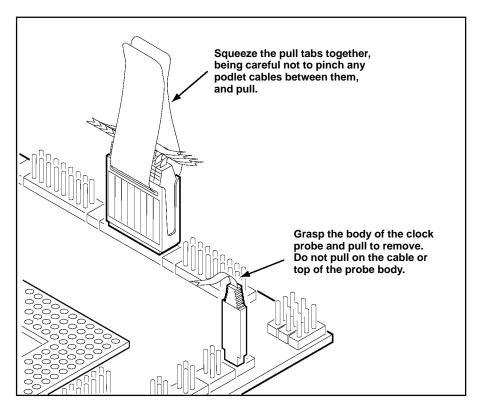

|                    | Removing a Clock Probe or 8-Channel Probe Podlet from the Interface Housing | C-19      |

|                    | Replacing a Clock Probe                                                     | C-20      |

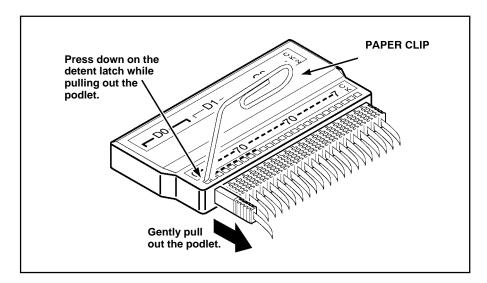

|                    | Removing 8-Channel Probe Podlets from the Podlet Holder                     | C-20      |

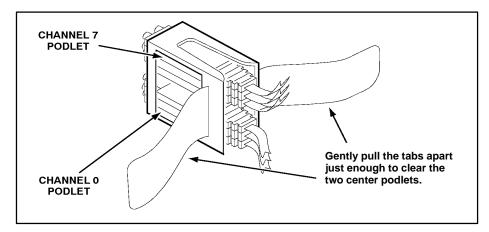

|                    | Replacing 8-Channel Probe Podlets                                           | C-21      |

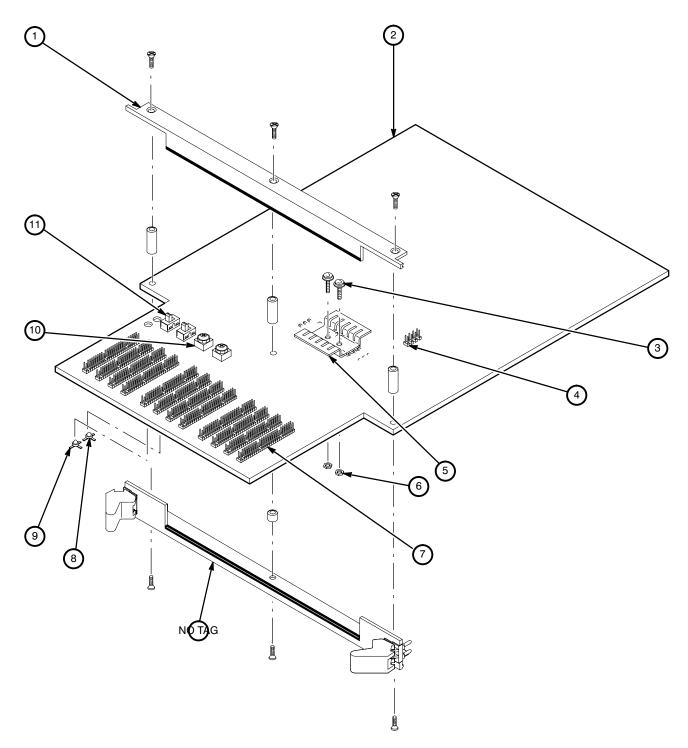

|                    | REPLACEABLE PARTS LIST                                                      | C-23      |

Index

## **List of Figures**

| Figure 1-1.  | DAS 9200 connected to a typical probe adapter.                              |  |

|--------------|-----------------------------------------------------------------------------|--|

| Figure 2-1.  | Sys Config menu with a variable-width module defined                        |  |

| Figure 2-2.  | Applying slot number labels                                                 |  |

| Figure 2-3.  | Connecting probes to the probe adapter                                      |  |

| Figure 2-4.  | Location of screw under yellow handles                                      |  |

| Figure 2-5.  | Switch locations on the probe adapter                                       |  |

| Figure 2-6.  | LED locations on the probe adapter.                                         |  |

| Figure 3-1.  | Save/Restore menu.                                                          |  |

| Figure 3-2.  | Default Clock menu for the Main bus module                                  |  |

| Figure 3-3.  | Default Clock menu for the Arb bus module                                   |  |

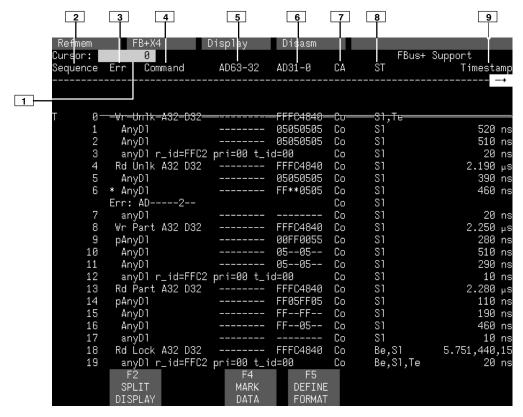

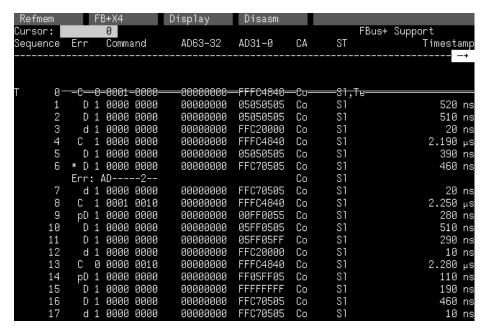

| Figure 4-1.  | Default Disassembly menu.                                                   |  |

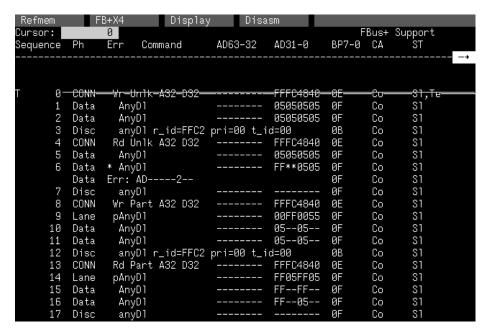

| Figure 4-2.  | Disassembly menu with Ph, AD31-0, and BP7-0 channel group values            |  |

| Figure 4-3.  | Disassembly menu with only CM information translated                        |  |

| Figure 4-4.  | Disassembly menu without asterisks to indicate AD bytes with parity errors. |  |

| Figure 4-5.  | Disassembly menu without dashes to indicate invalid AD bytes                |  |

| Figure 4-6.  | Disassembly menu without translating CM or AD information                   |  |

| Figure 4-7.  | Disassembly menu with only connect beats displayed                          |  |

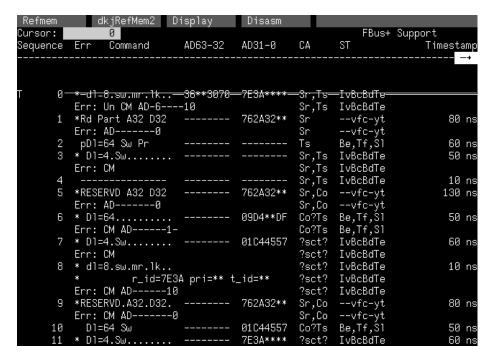

| Figure 4-8.  | Disassembly menu with ST symbols showing their various formats              |  |

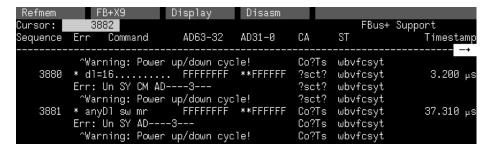

| Figure 4-9.  | Display of Power Up cycles                                                  |  |

| Figure 4-10. | Disassembly Format Definition overlay                                       |  |

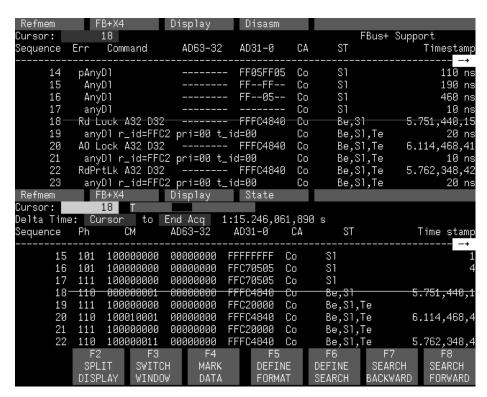

| Figure 4-11. | Disassembly and State split-screen display                                  |  |

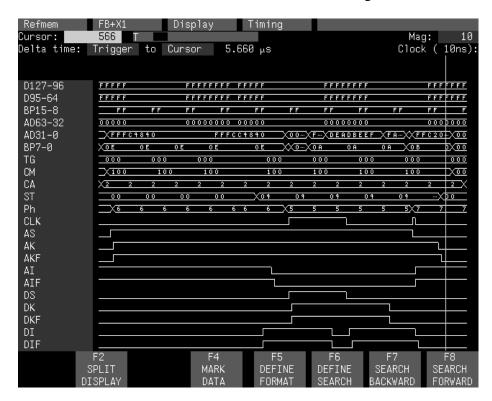

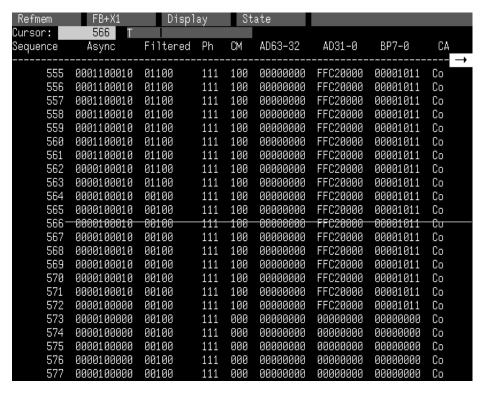

| Figure 5-1.  | Timing data displayed using the Fbus+_96 timing format file                 |  |

| Figure 5-2.  | State data                                                                  |  |

| Figure B-1.  | Futurebus+ bus timing for the Main bus.                                     |  |

| Figure B-2.  | Futurebus+ bus timing for the Arb bus.                                      |  |

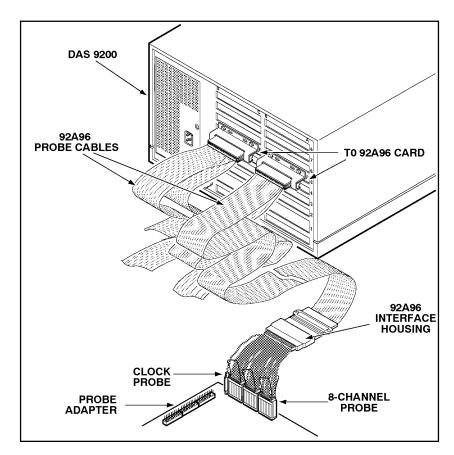

| Figure C-1.  | Overview of the DAS 9200 connected to a typical probe adapter               |  |

| Figure C-2.  | Switch locations on the probe adapter                                       |  |

| Figure C-3.  | LED locations on the probe adapter.                                         |  |

| Figure C-4.  | Disconnecting clock and 8-channel probes                                    |  |

| Figure C-5.  | Removing a probe podlet from the interface housing                          |  |

| Figure C-6.  | Ganging together the 8-channel probe podlets.                               |  |

## **List of Tables**

| Table 1-1  | Product Support                                                           | 1-1  |

|------------|---------------------------------------------------------------------------|------|

| Table 2-1  | Choosing the Correct Floppy Disk                                          | 2-3  |

| Table 2-2  | Sync/Async Switches Information                                           | 2-7  |

| Table 2-3  | Glitch Filter Delay Switch Positions                                      | 2-8  |

| Table 3-1  | Futurebus+ Supports and Supplied Setups                                   | 3-1  |

| Table 3-2  | FB+_Ph Symbol Table                                                       | 3-9  |

| Table 3-3  | CA Channel Group Bit Definitions                                          | 3-10 |

| Table 3-4  | FB+_Cap Symbol Table                                                      | 3-10 |

| Table 3-5  | ST Channel Group Bit Definitions                                          | 3-11 |

| Table 3-6  | FB+_Stat Symbol Table Definitions                                         | 3-12 |

| Table 4-1  | Connect Beat Transaction Types                                            | 4-4  |

| Table 4-2  | Data Transfer Lengths                                                     | 4-5  |

| Table 4-3  | Locked Commands                                                           | 4-5  |

| Table 4-4  | Extra Error Line Information                                              | 4-12 |

| Table 4-5  | Display Mode, Scroll By, and Highlight Fields and Beat-Select Functions . | 4-13 |

| Table 5-1  | Supplied Timing Format Definition Files and Uses                          | 5-3  |

| Table C-1  | Sync/Async Switches Information                                           | C-3  |

| Table C-2  | Glitch Filter Delay Switch Positions                                      | C-4  |

| Table C-3  | 92DM911 Ph Group Channel Assignments                                      | C-8  |

| Table C-4  | 92DM911 CM Group Channel Assignments                                      | C-8  |

| Table C-5  | 92DM911 AD63-32 Group Channel Assignments                                 | C-9  |

| Table C-6  | 92DM911 AD31-0 Group Channel Assignments                                  | C-10 |

| Table C-7  | 92DM911 BP7-0 Group Channel Assignments                                   | C-11 |

| Table C-8  | 92DM911 CA Group Channel Assignments                                      | C-11 |

| Table C-9  | 92DM911 ST Group Channel Assignments                                      | C-11 |

| Table C-10 | 92DM911 D127-96 Group Channel Assignments                                 | C-12 |

| Table C-11 | 92DM911 D95-64 Group Channel Assignments                                  | C-13 |

| Table C-12 | 92DM911 BP15-8 Group Channel Assignments                                  | C-14 |

| Table C-13 | 92DM911 TG Group Channel Assignments                                      | C-14 |

| Table C-14 | 92DM911 Async Group Channel Assignments                                   | C-15 |

| Table C-15 | 92DM911 Filtered Group Channel Assignments                                | C-15 |

| Table C-16 | 92DM911 ArbAsync Group Channel Assignments                                | C-16 |

| Table C-17 | 92DM911 ArbFiltd Group Channel Assignments                                | C-16 |

| Table C-18 | 92DM911 AC Group Channel Assignments                                      | C-17 |

| Table C-19 | 92DM911 AB Group Channel Assignments                                      | C-17 |

| Table C-20 | Podlet-to-Channel Color Code                                              | C-21 |

## Preface: GUIDE TO DAS 9200 DOCUMENTATION

The Digital Analysis System (DAS) 9200 documentation package provides the information necessary to install, operate, maintain, and service the DAS 9200. The DAS 9200 documentation consists of the following:

- a series of microprocessor-specific microprocessor support instructions that describe the various microprocessor support packages.

- a system user manual that includes a beginning user's orientation, a discussion of DAS 9200 system-level operation, and reference information such as installation procedures, specifications, error messages, and a complete system glossary.

- a series of **module user manuals** that describe each of the DAS 9200 acquisition, pattern generation, and optional I/O modules.

- an **on-line documentation** package that includes context-sensitive technical notes.

- a programmatic command language user manual that describes the set of programmatic commands available for remotely controlling the DAS 9200.

- a series of **application software user manuals** that describe the various application software packages.

- a **technician's reference manual** that helps a qualified technician isolate DAS 9200 problems to the individual module level and determine corrective action (including on-site removal and replacement of modules).

- a **verification and adjustment procedures manual** that allows a qualified technician to make necessary adjustments and verify specifications of the mainframe and modules.

- a series of **workbooks** that teach concepts about the DAS 9200 acquisition modules and pattern generation modules.

## GENERAL SAFETY SUMMARY/ DISASSEMBLERS

The general safety information in this summary is for operating and servicing personnel. Specific warnings and cautions can be found throughout the manual where they apply and may not appear in this summary. While using this product you may need to access parts of the DAS 9200 mainframe system; if so, read the General Safety Summary in your *DAS 9200 System User Manual* for warnings and cautions related to operating the mainframe system.

#### **TERMS IN THIS MANUAL**

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

#### TERMS AS MARKED ON EQUIPMENT

CAUTION indicates a hazard to property, including the equipment itself, and could cause minor personal injury.

## WARNING

WARNING indicates solely a personal injury hazard not immediately accessible as you read the marking.

DANGER indicates a personal injury hazard immediately accessible as you read the marking.

#### SYMBOLS AS MARKED ON EQUIPMENT

DANGER High Voltage Protective ground (earth) terminal

ATTENTION Refer to manual

#### **USE CARE WITH COVERS REMOVED**

To avoid personal injury, remove jewelry such as rings, watches, and other metallic objects before removing the cover. Do not touch exposed connections and components within the product while the power cord is connected.

#### **REMOVE FROM OPERATION**

If you have reason to believe that the instrument has suffered a component failure, do not operate the instrument until the cause of the failure has been determined and corrected.

#### **USE THE PROPER FUSE**

To avoid fire hazard, use only a fuse of the correct type, voltage rating, and current rating.

#### **REMOVE LOOSE OBJECTS**

During disassembly or installation procedures, screws or other small objects may fall to the bottom of the mainframe. To avoid shorting out the power supply, do not power on the instrument until such objects have been removed.

#### DO NOT OPERATE IN EXPLOSIVE ATMOSPHERES

To avoid explosion, do not operate this product in an explosive atmosphere unless it has been specifically certified for such operation.

## **Section 1: OVERVIEW**

This section provides basic information on the following:

- the 92DM911 Bus Support product

- software compatibility

- DAS 9200 configuration

- this manual

The 92DM911 Bus Support product disassembles data from systems that are based on the 12SU Hard Metric IEEE 896 Profiles A, B, and F Futurebus+ bus. The 92DM911 product runs on a DAS 9200 logic analyzer equipped with one, two, or three 92A96 Acquisition Modules.

The Futurebus+ bus is actually two buses: the Arbitrated Messages bus, and the Main bus. The 92DM911 product supports compelled transactions on a 32-, 64-, or 128-bit wide Main bus. The 92DM911 product does not acquire or display data for packet data beats.

The 92DM911 product acquires, disassembles, and displays data in the Disassembly display for the Main bus only. You can also display Main bus data in the State and Timing displays.

The product also acquires state data for the Arbitrated Messages bus. You can display acquired data from the Arbitrated Messages bus in the State or Timing displays.

Table 1-1 shows the number of 92A96 Modules you can have in your DAS 9200 system and the Futurebus+ buses they can support.

Table 1-1

Product Support

| No. of<br>Modules | Supported Futurebus+ Buses                                        |

|-------------------|-------------------------------------------------------------------|

| 1                 | Lower 32- or 64-bits of the Main bus only* or                     |

|                   | Arbitrated Messages bus only                                      |

| 2                 | 32-, 64-, or 128-bits of the Main bus only or                     |

|                   | Lower 32- or 64-bits of the Main bus* and Arbitrated Messages bus |

| 3                 | 32-, 64-, or 128-bits of the Main bus and Arbitrated Messages bus |

| *Asynchrono       | us control signals not available.                                 |

This product consists of software on a floppy disk, a probe adapter, and this manual. The software includes setup files, a demonstration reference memory, symbol tables, and a disassembler program. A complete list of accessories and options is provided at the end of *Appendix C: Service Information*.

A demonstration reference memory is provided so you can see an example of disassembled bus mnemonics. You can view the reference memory without connecting the DAS 9200 to your system under test. The reference memory is automatically installed on the DAS 9200 when you install the disassembler software. Directions for viewing this file are in Section 4: Acquiring and Viewing Disassembled Data.

To use this product efficiently, you need to have the following:

- knowledge of your Futurebus+ system

- knowledge of your DAS 9200 configuration and its operation

- this manual

- the DAS 9200 System User Manual

- the 92A96 Module User Manual, Tektronix, Inc. 1992

#### DAS 9200 SYSTEM SOFTWARE COMPATIBILITY

The 92DM911 Bus Support Product is compatible with the DAS 9200 System Software Release 2, Version 1.51 or higher, and DAS 92XTerm System Software Release 3, Version 1.2 or higher.

#### **DAS 9200 CONFIGURATION**

To use the bus support product, your DAS 9200 must be equipped with at least one 92A96 Module and four standard data acquisition probes.

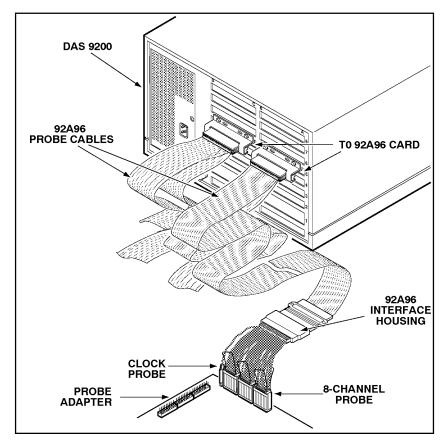

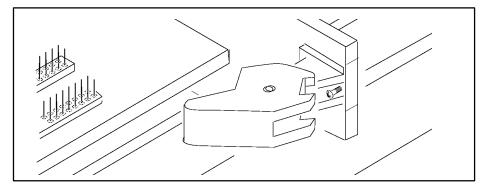

Figure 1-1 shows an overview of the DAS 9200 connected to a typical probe adapter.

Figure 1-1. DAS 9200 connected to a typical probe adapter.

#### **ABOUT THIS MANUAL**

This manual is based on the assumption that you are familiar with the operation of the DAS 9200 mainframe and the 92A96 Acquisition Module. Therefore, details about system software and how to move through the menu structure are not provided. An overview of those functions is provided so that you do not need to consult another manual.

This manual provides detailed information on how to do the following:

- connect to your system under test

- setup disassembler software and use it

- view acquired data

- maintain disassembler hardware

Read Section 5: General Purpose Analysis if you are going to acquire and view timing or state data for purposes other than disassembly.

### **Manual Conventions**

The following conventions are used in this manual:

- the term Arb bus refers to the Futurebus+ Arbitrated Messages bus signals.

- the term Main bus refers to the remaining Futurebus+ bus signals.

- the terms disassembler and disassembler software are used interchangeably in reference to the 92DM911 software that disassembles bus cycles into mnemonics and transaction types.

- the term system under test (SUT) is used to refer to the bus system from which data is being acquired.

- references to 92A96 Modules include all versions of those Modules unless otherwise noted.

## Section 2: INSTALLATION AND CONNECTIONS

This section describes how to do the following:

- configure the DAS 9200

- position the 92A96 Modules in the DAS 9200

- install the disassembler software

- connect the DAS 9200 to the system under test (SUT)

- configure the probe adapter

#### **CONFIGURING THE DAS 9200**

To acquire data from a 128-bit wide Main bus, two 92A96 Modules are required. They must be configured into one variable-width module.

When using a variable-width module, both 92A96 Modules must be positioned in adjacent DAS 9200 slots. The module in the higher-numbered slot is referred to as the HI module; the module in the lower-numbered slot is referred to as the LO module. You cannot use slots 1 or 8 when creating a variable-width module. The modules do not need to have the same memory depth.

Probe connections on the probe adapter board are labeled to identify which module and which probe group connects to them. For example, LO\_A0 indicates the A0 group from the LO Module.

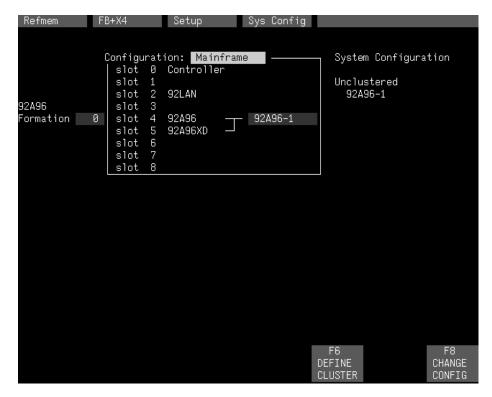

If acquiring data from a 128-bit wide Main bus, you should check the System Configuration menu to verify that the variable-width module is defined correctly. Figure 2-1 shows how the Sys Config menu looks when two 92A96 Modules are combined into a variable-width module.

Refer to your module user manual for additional information about variable-width modules, connecting probe cables, and positioning and installing 92A96 Modules.

Figure 2-1. Sys Config menu with a variable-width module defined.

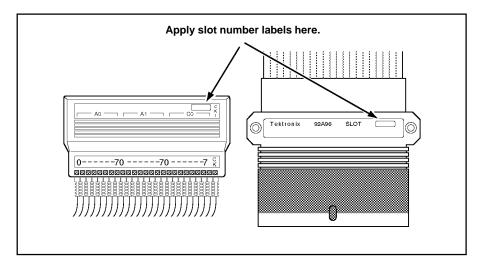

In a multimodule system, it is easier to identify which modules are connected to the probe adapter if slot number labels are applied to the 92A96 probe interface housings and DAS 9200 mainframe. Figure 2-2 shows how to apply slot number labels.

Figure 2-2. Applying slot number labels.

#### INSTALLING SOFTWARE

Before installing the bus application software, you should be aware that there are two different versions of DAS 9200 system software: the 9201T version and the 92XTerm version. The 9201T version allows you to operate the DAS 9200 from a 9201T terminal. The 92XTerm version allows you to operate the DAS 9200 in an X window on a workstation.

#### **NOTE**

To use the bus support package, you must install application software that is compatible with your DAS 9200 mainframe configuration and system software.

Three floppy disks are shipped with the 92DM911 bus support. To determine which floppy disk contains compatible application software, follow these steps:

- 1. Note the terminal type on which the DAS 9200 system software will run.

- 2. Power on the DAS 9200 mainframe or system, and press the Select Menu key.

- 3. Select the HW/SW Version menu in the Utilities column and press Return.

- 4. Look at the System Software line to find the version of system software loaded. Use Table 2-1 to choose the appropriate floppy disk to install.

Table 2-1 Choosing the Correct Floppy Disk

| Terminal Type                                                                                            | System Software Line Information* | Install Floppy Disk Labelled             |

|----------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------|

| 9200T/9201T                                                                                              | Release 2, Version 1.50           | DAS 9200 Application Software - 92DM911  |

| 9200T/9201T                                                                                              | Release 3, Version 1.20           | DAS 9201T Application Software - 92DM911 |

| X window on a workstation                                                                                | Release 3, Version 1.20           | DAS 92XTERM Application SW - 92DM911     |

| *Version numbers shown are the lowest versions supported; higher version numbers within the same release |                                   |                                          |

\*Version numbers shown are the lowest versions supported; higher version numbers within the same release are also supported.

If you have two types of DAS 9200 system software (9201T and 92XTerm), and you switch between the two, you must install compatible application software on each system.

If you try to install application software onto an incompatible system using DAS 9200 System Software Release 3, V1.1 or greater, an error message displays.

If you try to install application software onto an incompatible system using DAS 9200 System Software Release 3, V1.0 or lower, the system will install the software but it will not operate properly when you try to use it.

Install the disassembler software onto the DAS 9200 as follows:

- 1. Power up the DAS 9200 mainframe.

- 2. Insert the appropriate disk into the DAS 9200's floppy drive.

- 3. Press the Select Menu key and select the Disk Services menu.

- 4. Select Install Application in the Operation field of the menu.

- 5. Press F8: EXECUTE OPERATION and follow the on-screen prompts.

#### **NOTE**

After each install and load operation, a message appears on the screen informing you the operation succeeded or failed. If the message tells you the operation failed, you may need to remove applications or files from the hard disk and try installing or loading again. If the operation fails again, refer to Appendix A: Error Messages and Disassembly Problems.

#### CONNECTING TO THE SYSTEM UNDER TEST

Before you connect to the SUT, you must connect the standard probes to the 92A96 Module.

If your Futurebus+ system uses live-insertion filtering, refer to the description of *Jumpers* at the end of this section for information on live-insertion filtering and J4.

To connect the DAS 9200 to the SUT, do the following:

1. Turn off power to your SUT. It is not necessary to turn off power to the DAS 9200.

Static discharge can damage the probe adapter, the probes, or the 92A96 Module. To prevent static damage, handle the probe adapter, probes, and modules only in a static-free environment.

Always wear a grounding wrist strap or similar device while handling the probe adapter and Futurebus+ boards.

- 2. Attach a grounding strap between the ground jack on the back of the DAS 9200 and a ground point on the SUT.

- 3. To discharge your stored static electricity, touch the ground jack located on the back of the DAS 9200. Then, touch any of the ground pins of the probe adapter to discharge stored static electricity from the probe adapter.

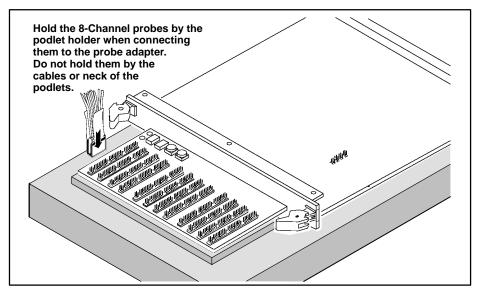

- 4. Place the probe adapter onto a large piece of antistatic shipping foam to support the probe adapter as shown in Figure 2-3. This prevents the circuit board and its components from flexing.

- 5. To keep the probe adapter from teetering on the edge of the front panel as you connect the probes, place additional non-conductive material (such as foam) under the area to which the probes attach.

- 6. To connect the probes for each module, refer to Figure 2-3 and line up each probe with the corresponding section name printed on the probe adapter circuit board. The interface housing label indicates the group to which each clock and 8-channel probe connects. Ground pins are indicated on the board.

Figure 2-3. Connecting probes to the probe adapter.

## E CAUTION §

Live insertion of the probe adapter is **not** supported. To prevent damage to the probe adapter and Futurebus+ system, plug the probe adapter into the backplane when the Futurebus+ system is powered off.

Failure to correctly place the probe adapter into the Futurebus+ backplane may damage the Futurebus+ system once power is applied.

After connecting the clock and 8-channel probes, you can install the probe adapter into your SUT as you would normally install any other Futurebus+ board. You can use the two yellow handles on the front panel of the probe adapter as needed when you install or remove the probe adapter.

To ensure that the probe adapter board is secure, tighten the screws under the yellow handles. Figure 2-4 shows the location of these screws.

Figure 2-4. Location of screw under yellow handles.

#### CONFIGURING THE PROBE ADAPTER

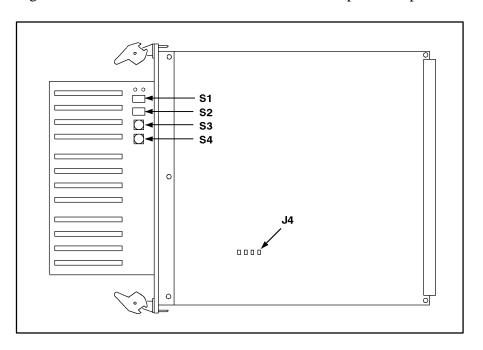

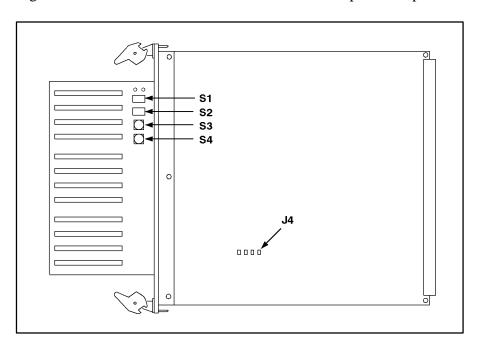

There are two slide switches and two rotary switches on the probe adapter. The two slide switches are used to configure the probe adapter to acquire data from the Main or Arb buses for either synchronous (disassembly) or asynchronous (timing analysis) operation. One of the rotary switches is set to match the data path width of the Futurebus+system backplane. The other rotary switch sets the glitch filter delay on the probe adapter.

## **Sync/Async Switches**

The Sync/Async switches (S1 and S2) should be placed in the Sync position to acquire disassembly data, and in the Async position to acquire timing data. Use S1 to set probe adapter operation for the Main bus and S2 to set probe adapter operation for the Arb bus. Table 2-2 shows how to position these switches depending on the type of clocking you're using and the type of display you want to view.

Table 2-2 Sync/Async Switches Information

| Switch Positions    | Clocking  | Display Menu                  |  |

|---------------------|-----------|-------------------------------|--|

| S1, Main bus        |           |                               |  |

| Sync (Disassembly)  | Custom    | Disassembly, Timing, or State |  |

|                     | Internal* | Timing or State               |  |

| Async (Timing)      | Internal  | Timing or State               |  |

| S2, Arb bus         |           |                               |  |

| Sync (Disassembly)† | External  | Disassembly†, Timing or State |  |

|                     | Internal* | Timing or State               |  |

| Async (Timing)      | Internal  | Timing or State               |  |

<sup>\*</sup>Only useful for verifying probe adapter operation.

Figure 2-5 shows the locations of S1 and S2 on the probe adapter.

Figure 2-5. Switch locations on the probe adapter.

<sup>†</sup>Display of Arb bus data with Main bus disassembly requires clustering and correlating of the Arb bus module with the Main bus module.

### **Glitch Filter Delay Switch**

You can set the Glitch Filter Delay switch, S3, to an appropriate setting to match the characteristics of your Futurebus+ system backplane. Table 2-3 shows how to position this switch.

Table 2-3

Glitch Filter Delay Switch Positions

| Switch Position                                 | Nominal Delay* |  |

|-------------------------------------------------|----------------|--|

| 0                                               | 13 ns          |  |

| 1                                               | 20 ns          |  |

| 2                                               | 27 ns          |  |

| 3                                               | 35 ns          |  |

| *Twice the one-way backplane propagation delay. |                |  |

#### **NOTE**

The operation of the Main and Arb bus logic on the probe adapter is **not** affected by this switch setting. Refer to Appendix C for more information about this switch.

Figure 2-5 shows the location of S3 on the probe adapter.

#### **Data Path Width Switch**

You must set the Data Path Width switch, S4, to match the width of the data bus portion of the Futurebus+ system backplane to which the probe adapter connects. Switch positions are for 32-, 64-, and 128-bit wide data buses.

Figure 2-5 shows the location of S4 on the probe adapter.

## **Jumpers**

Three jumpers, J1, J2, and J3, on the probe adapter should always be left open (no jumper). You cannot change the position of these jumpers and expect normal operation.

The last jumper, J4, controls whether live-insertion filtering is used in the acquisition of the AS\* and DS\* signals of the Main bus. These signals control the operation of the Main bus circuitry on the probe adapter. When J4 is not connected, filtering does not occur. When J4 is connected, filtering does occur.

Typically, J4 will not be connected unless you are using the probe adapter in a Futurebus+ system in which boards are installed and removed while the system is powered on. If you install or remove boards in your Futurebus+ system with power applied, then you should place a jumper on J4. Refer to Appendix C for more information on J4.

Live insertion of the probe adapter is **not** supported. To prevent damage to the probe adapter and Futurebus+ system, plug the probe adapter into the backplane when the Futurebus+ system is powered off.

#### **NOTE**

Do not install or remove J4 while the probe adapter is connected to a Futurebus+ system that is powered on; doing so may cause the Main bus circuitry on the probe adapter to enter an improper state.

If you change the jumper when the Futurebus+ system is powered on, you may have to reset the probe adapter circuitry.

The probe adapter can be reset in two ways. You can either power the Futurebus+ system off and then on, or you can momentarily short the POWERED signal of the probe adapter to ground. Table C-16 shows the channel assignment of the POWERED signal.

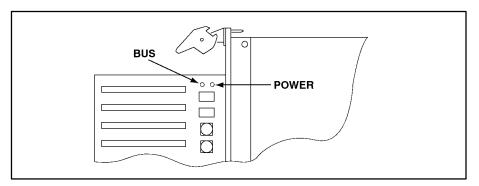

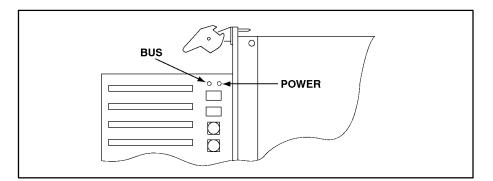

#### LED INDICATORS

There are two LEDs on the probe adapter. One lights when power is applied to the probe adapter, and the other lights when there is activity on the Futurebus+ bus.

The Power LED is red when the probe adapter is powered on. The Bus LED is yellow when either the AK\* signal on the Main bus or the AP\* signal on the Arb bus is asserted.

Figure 2-6 shows the location of these LEDs on the probe adapter.

Figure 2-6. LED locations on the probe adapter.

# Section 3: SETTING UP DISASSEMBLER SOFTWARE

This section tells how to prepare the disassembler software for acquiring data and discusses the following:

- supplied setups

- creating new setups

- channel groups and assignments

- · changes that affect disassembly

- clocking

- symbols

- triggering

Before you acquire and disassemble data, you need to specify setups for clocking, triggering, and using symbols. The disassembly software provides default values for each of these setup controls, but you can change them as needed.

Table 3-1 shows the number of 92A96 Modules, the Futurebus+ buses they can support, and the name of the support or supplied setup you can use with each.

Table 3-1

Futurebus+ Supports and Supplied Setups

| No. of<br>Modules       | Supported Futurebus+ Buses                            | Name of Support or Supplied Setup |

|-------------------------|-------------------------------------------------------|-----------------------------------|

| 1                       | Lower 64-bits* of the Main bus only†                  | FBus64 support                    |

|                         | Arb bus only                                          | FB_1-A96 setup                    |

| 2                       | 128-bits* of the Main bus only                        | FBus+ support                     |

|                         | Lower 64-bits* of the Main bus† and Arb bus           | FB_2-A96 setup                    |

| 3                       | 128-bits* of the Main bus and Arb bus                 | FB_3-A96 setup                    |

| *Or less<br>†Asynchrono | us control signals not available for timing analysis. |                                   |

When you select a support type in the Software Support field of the 92A96 Configuration setup menu, the Channel, Clock, and Trigger menus are set up to support the probe adapter signals and switch settings. Acquired data is also disassembled when viewed in the Disassembly display.

A supplied setup allows you to restore previously saved setups for the Configuration, Channel, Clock, and Trigger menus. Clocking choices and disassembler support depend on the type of software support selected in the restored Configuration menu.

The two support types shown in Table 3-1 configure the DAS 9200 to acquire data from the Main bus only.

The three supplied setups shown in Table 3-1 configure the DAS 9200 to acquire data from the Arb bus only, or from both the Arb and Main buses. The Software Support field in the Configuration menu for the module acquiring Arb bus data is set to General Purpose. The Software Support field in the Configuration menu for the module acquiring Main bus data is set to either FBus+ or FBus64.

#### MODULE SUPPORT AND SUPPLIED SETUPS

The bus support product supplies the disassembler software and setup files for the module(s) to use to acquire and display Futurebus+ bus activity. Setup files are supplied for the Channel, Clock, and Trigger menus. Symbol files are supplied for displaying data and for use in the Trigger menu as word recognizer values. Timing format files are also provided for the Timing menu when performing timing analysis (described in Section 5).

You can select the disassembler (and its associated setup files) by selecting a type of Futurebus+ support, or by restoring a supplied setup file. Refer to the discussions on *Loading Support Software* and *Restoring Supplied Setups* later in this section for more information.

When there are two or three 92A96 Modules in adjacent slots, they are automatically formed into a variable-width module by the system software at power-on. You may have to reconfigure a variable-width module prior to selecting an appropriate software support in the 92A96 Configuration menu. If you restore a supplied cluster setup, the reconfiguration is done for you. Refer to the discussion of the System Configuration menu in the *DAS 9200 System User Manual* for details on how to reconfigure a variable-width module.

When you restore a supplied Futurebus+ multimodule setup, the DAS 9200 automatically does the following:

- reconfigures 92A96 Modules if the setup requires a variable-width module

- clusters and correlates 92A96 Modules if the setup requires a variable-width module clustered and correlated with another module

- selects the appropriate type of support for each of the modules

- defines two communication signals for use in the trigger programs of the modules called MainToArb and ArbToMain

- defines triggering for each module using the communication signals

- provides two predefined Timing Format Definition files, called FBus+\_96, and FB+Arb\_96

### Full Main Bus and Arb Bus Supplied Setup

The FB\_3-A96 setup requires three 92A96 Modules. When the setup is restored, a variable-width 92A96 Module is defined for the Main bus, which is clustered and correlated with a single 92A96 Module for the Arb bus. This setup configures the Channel, Clock, and Trigger menus of the DAS 9200 to acquire data from 128-bits (or less) of the Main bus and from the Arb bus.

## Partial Main Bus and Arb Bus Supplied Setup

The FB\_2-A96 setup requires two 92A96 Modules. When the setup is restored, the module for the Main bus is clustered and correlated with the module for the Arb bus. This setup also configures the Channel, Clock, and Trigger menus of the DAS 9200 to acquire data from 64-bits (or less) of the Main bus and from the Arb bus.

## **Full Main Bus Only Support**

The FBus+ support software requires two 92A96 Modules formed into a variable-width module. When you access the Configuration menu and select Fbus+ in the Software Support field, the Channel, Clock, and Trigger menus for the variable-width module are set up to acquire data from 128-bits (or less) of the Main bus only.

## **Partial Main Bus Only Support**

The FBus64 support software requires one 92A96 Module. When you access the Configuration menu and select Fbus64 in the Software Support field, the Channel, Clock, and Trigger menus for the module are set up to acquire data from the lower 64-bits (or less) of the Main bus only.

## **Arb Bus Only Supplied Setup**

The FB\_1-A96 setup requires one 92A96 Module. When the setup is restored, it configures the Channel, Clock, and Trigger menus to acquire data from the Arb bus only.

#### LOADING SUPPORT SOFTWARE

To load the FBus+ or FBus64 support, follow these steps:

- 1. Press the Menu Select key, select the Main bus module, select its Configuration menu, and press Return.

- 2. Select FBus+ or FBus64 support in the Software Support field.

- 3. Press F8: EXECUTE OPERATION.

When you load the support software, the Channel, Clock, and Trigger menus are automatically set up to acquire Main bus data from your Futurebus+ system. You can change the setups in the Clock and Trigger menus as needed. Refer to *Channel Groups and Assignments* in this section for information on what can be changed in the Channel menu.

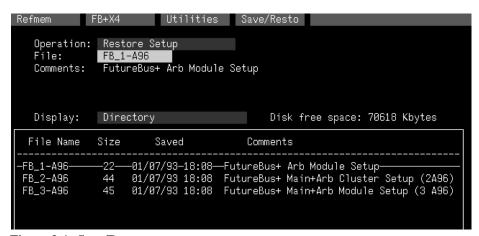

#### RESTORING SUPPLIED SETUPS

To restore a supplied setup, refer to Figure 3-1 and follow these steps:

- 1. Press the Menu Select key, select the Save/Restore menu, and press Return.

- 2. Select Restore Setup (or Restore Partial Setup) in the Operation field.

- 3. Select the desired setup in the File field. The support software supplies three setup files: FB\_1-A96, FB\_2-A96, and FB\_3-A96.

- 4. Press F8: EXECUTE OPERATION.

Figure 3-1. Save/Restore menu.

If you restored the FB\_2-A96 or FB\_3-A96 setup, the DAS 9200 automatically configures itself for multimodule operation. Refer to *Module Support and Supplied Setups* for a description of multimodule operation.

If the current placement of the data acquisition modules does not match that of the selected setup, the Restore Formation overlay appears. Press the F4: PLACE MODULES key or use the overlay to assign the module setups to the current placement of the modules.

If you are using 92A96D Modules when you restore a setup, the default acquisition memory depth is set to 8K. To use a greater memory depth, select a higher value in the Acquisition Memory Size field of the Configuration menu for each deep module.

#### CREATING MULTIMODULE SETUPS

You can create setups that meet the needs of your specific application. For example, you can create a setup that provides additional intermodule communication signals for use in complex trigger programs, or a setup to acquire data from multiple buses or other devices.

As you create a multimodule setup, keep in mind that Main and Arb bus modules must communicate with (signal to) each other, and that they must also start acquiring data at the same time. Therefore, you must set up the Main and Arb bus modules to be clustered and correlated, and you must also define signals for triggering purposes.

Before you can create a new setup using the Futurebus+ disassembler, you must first install the software and its associated files. Refer to the discussion on *Installing Software* in Section 2 for directions on how to do this.

The steps generally necessary to create your own setup are as follows:

- configure the DAS 9200 (if acquiring 128-bit wide Main bus data)

- restore an appropriate supplied setup or select a type of support

- name the modules

- cluster the modules

- correlate the modules

- define signals

- use signals in trigger programs (Trigger menu)

- set the start mode to ATE (Cluster menu)

Refer to your *DAS 9200 System User Manual* for information on how to perform these steps.

To restore a supplied setup, refer to the description of *Restoring Supplied Setups* earlier in this section.

#### CHANNEL GROUPS AND ASSIGNMENTS

The disassembler software automatically defines the channel groups for the Futurebus+ bus support. The channel groups for the Main bus are Ph, CM, AD63-32, AD31-0, BP7-0, CA, ST, D127-96, D95-64, BP15-8, TG, Async, and Filtered. The channel groups for the Arb bus are ArbAsync, ArbFiltered, AC, AB, and S1.

For the FBus+ disassembler to operate properly, the names and channel assignments of all Main groups above (except Async and Filtered) must not be changed. For the FBus64 disassembler, the name and channel assignments of the Ph, CM, AD63-32, AD31-0, BP7-0, CA, and ST channel groups must not be changed.

You can use channels from groups not used for disassembly to connect to other signals in your SUT. For example, you can use individual channels from the Async and Filtered groups to make other connections because these groups are not used for disassembly. You can also use channels from the AD63-32, BP7-4, D127-96, D95-64, BP15-8, and TG groups if you are not going to acquire bus data using these groups. If you want to know which signal is in which group, refer to the channel assignment tables in *Appendix C: Service Information*. Channel assignments are also shown in the Channel menu.

#### CHANGES THAT AFFECT DISASSEMBLY

You can change part of the default setups for the 92A96 Modules. However, keep in mind that if you change the threshold voltage (normally TTL, 1.5 V) or display polarity (normally +), the disassembled data will be affected.

#### CLOCKING

You can use the Clock menu to set clocking choices to control data sampling. The 92DM911 software offers a customized clocking selection for the Main bus of the Futurebus+ system. This clocking choice (Custom) is the default selection whenever you select the FBus64 or FBus+ Support in the Configuration menu.

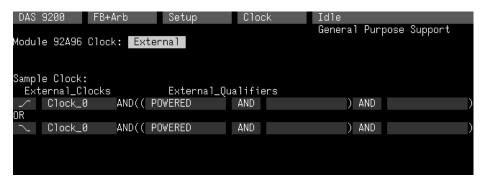

Custom clocking is also the default selection for the Main bus when you restore any of the three supplied setup files. No Custom clocking selection is available for the Arb bus because there is no disassembler for the Arb bus. The Arb bus uses External clocking as the default selection when you restore any of the supplied setup files.

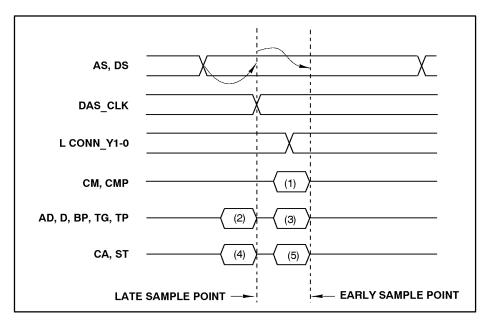

A description of how bus activity is sampled by the probe adapter is found in Appendix B.

#### **Main Bus**

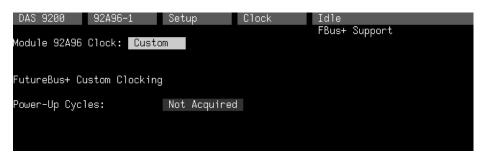

The 92DM911 software provides two modes for acquiring Main bus data: Power-Up Cycles Acquired or Power-Up Cycles Not Acquired. The default is Power-Up Cycles Not Acquired. You can change the clocking mode by changing the Power-Up Cycles option field in the Clock menu. Figure 3-2 shows the default Clock menu setup for the Main bus module.

A power-up cycle is any cycle that occurs while the POWERED signal is false. This occurs when the Futurebus+ system is being powered-up or powered-down.

Figure 3-2. Default Clock menu for the Main bus module.

Disassembly will not be correct with the Internal or External clocking modes. Refer to *Section 4: General Purpose Analysis* for a description of using these other clock selections with this bus support package.

To select the clocking mode, do the following:

- 1. Press the Select Menu key.

- 2. Select the Clock menu for the Main bus module you want to use.

- 3. Select Custom clocking (the default with either support type selected in the Configuration menu).

- 4. Move the cursor to the Power-Up Cycles field and select one of the following types of clocking:

- Acquired

- Not Acquired

#### **Arb Bus**

No Custom clocking selection is available for the Arb bus because there is no disassembler for the Arb bus. The Arb bus uses External clocking as the default selection when you restore any of the supplied setup files. Figure 3-3 shows the default Clock menu for the Arb bus module.

Figure 3-3. Default Clock menu for the Arb bus module.

#### **SYMBOLS**

Symbols can represent a set of specific channel group values or a range of channel group values (defined by upper and lower bounds).

You can use symbol tables to display channel group information symbolically in the State and Disassembly menus and to control triggering. There are three symbol table files supplied by the disassembler software to replace specific channel group values. Refer to *Triggering* in this section and *Displaying Channel Groups Symbolically* in Section 4 for more information on displaying symbolic values.

You can use the Symbol Editor to copy, rename, save, and modify any of the supplied symbol tables to suit your needs. Refer to *Copying and Editing Supplied Symbol Tables* later in this section for a description of how to do this.

When used in the State or Disassembly display, DAS 9200 system software searches for the first match value found in the symbol table and displays the corresponding symbol name.

Table 3-2 shows the name and bit pattern for the symbols in the file FB+\_Ph, the Ph (phase) channel group symbol table.

Table 3-2 FB+\_Ph Symbol Table

|        | Ph Group<br>Value               |        | Ph Group<br>Value               |

|--------|---------------------------------|--------|---------------------------------|

| Symbol | POWERED<br>L_CONN_1<br>L_CONN_0 | Symbol | POWERED<br>L_CONN_1<br>L_CONN_0 |

| UnPd   | 0 X X                           | 0X1    | 0 X 1                           |

| Lane   | 1 0 0                           | 00X    | 0 0 X                           |

| Data   | 1 0 1                           | 000    | 0 0 0                           |

| CONN   | 1 1 0                           | 001    | 0 0 1                           |

| Disc   | 1 1 1                           | 01X    | 0 1 X                           |

| XXX    | XXX                             | 010    | 0 1 0                           |

| XX0    | X X 0                           | 011    | 0 1 1                           |

| XX1    | X X 1                           | 1XX    | 1 X X                           |

| X0X    | X 0 X                           | 1X0    | 1 X 0                           |

| X00    | X 0 0                           | 1X1    | 1 X 1                           |

| X01    | X 0 1                           | 100    | 1 0 X                           |

| X1X    | X 1 X                           | 100    | 1 0 0                           |

| X10    | X 1 0                           | 101    | 1 0 1                           |

| X11    | X 1 1                           | 11X    | 1 1 X                           |

| 0XX    | 0 X X                           | 110    | 1 1 0                           |

| 0X0    | 0 X 0                           | 111    | 1 1 1                           |

The UnPd symbol signifies a beat obtained during SUT power on or power off. The Lane symbol signifies the first data beat (lane deselection specification) of a partial transaction. The Data symbol signifies any other data beat. The CONN symbol signifies a connect beat. The Disc symbol signifies a disconnect beat.

Table 3-3 shows the signals that make up the CA group, and the meaning of each bit when it is asserted.

Table 3-3 CA Channel Group Bit Definitions

| Signal<br>Name | Abbreviation in Symbol and Meaning When Asserted |

|----------------|--------------------------------------------------|

| CA_2           | Sr, a split response                             |

| CA_1           | Co, a compelled transaction                      |

| CA_0           | Ts, transmit speed low                           |

Table 3-4 shows the name and bit pattern for the symbols in the file FB+\_Cap, the CA channel group symbol table.

Table 3-4 FB+\_Cap Symbol Table

|                                                      | CA Group<br>Value    |        | CA Group<br>Value    |        | CA Group<br>Value    |  |  |

|------------------------------------------------------|----------------------|--------|----------------------|--------|----------------------|--|--|

| Symbol                                               | CA_2<br>CA_1<br>CA_0 | Symbol | CA_2<br>CA_1<br>CA_0 | Symbol | CA_2<br>CA_1<br>CA_0 |  |  |

|                                                      | 0 0 0                | X00    | X 0 0                | 010    | 0 1 0                |  |  |

| Ts                                                   | 0 0 1                | X01    | X 0 1                | 011    | 0 1 1                |  |  |

| Со                                                   | 0 1 0                | X1X    | X 1 X                | 1XX    | 1 X X                |  |  |

| Co?Ts†                                               | 0 1 1                | X10    | X 1 0                | 1X0    | 1 X O                |  |  |

| Sr                                                   | 1 0 0                | X11    | X 1 1                | 1X1    | 1 X 1                |  |  |

| Sr, Ts                                               | 1 0 1                | 0XX    | 0 X X                | 10X    | 1 0 X                |  |  |

| Sr, Co                                               | 1 1 0                | 0X0    | 0 X 0                | 100    | 1 0 0                |  |  |

| ?sct?†                                               | 1 1 1                | 0X1    | 0 X 1                | 101    | 1 0 1                |  |  |

| XXX                                                  | ххх                  | 00X    | 0 0 X                | 11X    | 1 1 X                |  |  |

| XX0                                                  | X X 0                | 000    | 0 0 0                | 110    | 1 1 0                |  |  |

| XX1                                                  | X X 1                | 001    | 0 0 1                | 111    | 1 1 1                |  |  |

| X0X                                                  | X 0 X                | 01X    | 0 1 X                |        |                      |  |  |

| †Not expected in normal Futurebus+ system operation. |                      |        |                      |        |                      |  |  |

Table 3-5 shows the signals that make up the ST group, the meaning of each bit when it is asserted, and the two- or one-letter abbreviation used in the symbol name.

Table 3-5 ST Channel Group Bit Definitions

| Signal<br>Name | Meaning When Asserted | 2-Letter<br>Abbreviation | 1-Letter<br>Abbreviation |  |

|----------------|-----------------------|--------------------------|--------------------------|--|

| ST_7           | Wait                  | Wt                       | w                        |  |

| ST_6           | Beat Error            | Be                       | b                        |  |

| ST_5           | Intervention          | lv                       | V                        |  |

| ST_4           | Transaction Flag      | Tf                       | f                        |  |

| ST_3           | Broadcast/Broadcall   | Вс                       | С                        |  |

| ST_2           | Selected              | SI                       | s                        |  |

| ST_1           | Busy or End of Data   | Bs/Ed<br>or Bd           | у                        |  |

| ST_0           | Transaction Error     | Te                       | t                        |  |

Table 3-6 shows the name and bit pattern for the symbols in the file FB+\_Stat, the ST channel group symbol table.

As can be seen, the two-letter abbreviation will display for all asserted bits, separated by commas whenever there is enough space on the display to do so. As more bits are asserted, the commas will not display. And, as even more bits are asserted, only the one-letter abbreviation will display.

Although the meaning of ST\_1 depends on when it was first asserted in the transaction (busy when asserted during a connect beat and end-of-data otherwise), the symbolic display of the ST channel group is only based on the value of the ST signals without consideration for the type of beat.

You may need to add additional symbols to a copy of the file to allow other ST values with several don't care bits to be used for triggering. Refer to *Copying and Editing the Supplied Symbol Tables* in this section for information on how to do this.

Table 3-6 FB+\_Stat Symbol Table Definitions

|            | ST Group Value                                   |                |           | ST Group Value                      |                 |            | ST Group Value         |         |

|------------|--------------------------------------------------|----------------|-----------|-------------------------------------|-----------------|------------|------------------------|---------|

|            | ST_7 ST_3<br>ST_6 ST_2<br>ST_5 ST_1<br>ST_4 ST_0 |                |           | ST_7 ST_3<br>ST_6 ST_2<br>ST_5 ST_1 |                 |            | ST_7 ST_3<br>ST_6 ST_2 |         |

| Symbol     | ST_5<br>ST_5<br>ST_                              | ST_1<br>4 ST 0 | Symbol    | ST_5<br>ST_5<br>ST_                 | ST_1<br>_4 ST_0 | Symbol     | ST_5<br>ST_5<br>ST_    | ST 1    |

| - Cymiller | 0 0 0 0                                          | 0 0 0 0        | Iv        | 0 0 1 0                             | 0 0 0 0         | Be         | 0 1 0 0                | 0 0 0 0 |

| Te         | 0 0 0 0                                          | 0 0 0 1        | Iv,Te     | 0 0 1 0                             | 0 0 0 0         | Be,Te      | 0100                   | 0 0 0 0 |

| Bs/Ed      | 0 0 0 0                                          | 0 0 1 0        | Iv, Bs/Ed | 0 0 1 0                             | 0 0 1 0         | Be,Bs/Ed   | 0 1 0 0                | 0 0 1 0 |

| Bs/Ed,Te   | 0 0 0 0                                          | 0 0 1 1        | Iv,Bd,Te  | 0 0 1 0                             | 0 0 1 1         | Be,Bd,Te   | 0 1 0 0                | 0 0 1 1 |

| S1         | 0 0 0 0                                          | 0 1 0 0        | Iv,Sl     | 0 0 1 0                             | 0 1 0 0         | Be,Sl      | 0 1 0 0                | 0 1 0 0 |

| S1,Te      | 0 0 0 0                                          | 0 1 0 0        | Iv,S1,Te  | 0 0 1 0                             | 0 1 0 1         | Be,S1,Te   | 0 1 0 0                | 0 1 0 0 |

| S1,Bs/Ed   | 0 0 0 0                                          | 0 1 0 1        | Iv,S1,FC  | 0 0 1 0                             | 0 1 1 0         | Be, S1, Bd | 0 1 0 0                | 0 1 0 1 |

| S1,Bd,Te   | 0 0 0 0                                          | 0 1 1 1        | IvS1BdTe  | 0 0 1 0                             | 0 1 1 1         | BeS1BdTe   | 0100                   | 0 1 1 1 |

| Bc         | 0 0 0 0                                          | 1 0 0 0        | Iv,Bc     | 0 0 1 0                             | 1 0 0 0         | Be,Bc      | 0 1 0 0                | 1 0 0 0 |

| Bc,Te      | 0 0 0 0                                          | 1 0 0 1        | Iv,Bc,Te  | 0 0 1 0                             | 1 0 0 1         | Be,Bc,Te   | 0 1 0 0                | 1 0 0 1 |

| Bc, Bs/Ed  | 0 0 0 0                                          | 1 0 1 0        | Iv,Bc,Rd  | 0 0 1 0                             | 1 0 1 0         | Be,Bc,Bd   | 0 1 0 0                | 1 0 1 0 |

| Bc,Bd,Te   | 0 0 0 0                                          | 1 0 1 1        | IvBcBdTe  | 0 0 1 0                             | 1 0 1 1         | BeBcBdTe   | 0 1 0 0                | 1 0 1 1 |

| Bc,S1      | 0 0 0 0                                          | 1 1 0 0        | Iv,Bc,S1  | 0 0 1 0                             | 1 1 0 0         | Be,Bc,S1   | 0 1 0 0                | 1 1 0 0 |

| Bc,Sl,Te   | 0 0 0 0                                          | 1 1 0 1        | IvBcSlTe  | 0 0 1 0                             | 1 1 0 1         | BeBcSlTe   | 0 1 0 0                | 1 1 0 1 |

| Bc,S1,Bd   | 0 0 0 0                                          | 1 1 1 0        | IvBcS1Bd  | 0 0 1 0                             | 1 1 1 0         | BeBcS1Bd   | 0 1 0 0                | 1 1 1 0 |

| BcS1BdTe   | 0 0 0 0                                          | 1 1 1 1        | v-csyt    | 0 0 1 0                             | 1 1 1 1         | -bcsyt     | 0 1 0 0                | 1 1 1 1 |

| Tf         | 0 0 0 1                                          | 0 0 0 0        | Iv,Tf     | 0 0 1 1                             | 0 0 0 0         | Be,Tf      | 0 1 0 1                | 0 0 0 0 |

| Tf,Te      | 0 0 0 1                                          | 0 0 0 1        | Iv,Tf,Te  | 0 0 1 1                             | 0 0 0 1         | Be,Tf,Te   | 0 1 0 1                | 0 0 0 1 |

| Tf,Bs/Ed   | 0 0 0 1                                          | 0 0 1 0        | Iv,Tf,Bd  | 0 0 1 1                             | 0 0 1 0         | Be,Tf,Bd   | 0 1 0 1                | 0 0 1 0 |

| Tf,Bd,Te   | 0001                                             | 0 0 1 1        | IvTfBdTe  | 0 0 1 1                             | 0 0 1 1         | BeTfBdTe   | 0 1 0 1                | 0 0 1 1 |

| Tf,S1      | 0001                                             | 0 1 0 0        | Iv,Tf,Sl  | 0 0 1 1                             | 0 1 0 0         | Be,Tf,Sl   | 0 1 0 1                | 0 1 0 0 |

| Tf,S1,Te   | 0001                                             | 0 1 0 1        | IvTfSlTe  | 0 0 1 1                             | 0 1 0 1         | BeTfSlTe   | 0 1 0 1                | 0 1 0 1 |

| Tf,S1,Bd   | 0 0 0 1                                          | 0 1 1 0        | IvTfS1Bd  | 0 0 1 1                             | 0 1 1 0         | BeTfS1Bd   | 0 1 0 1                | 0 1 1 0 |

| TfS1BdTe   | 0001                                             | 0 1 1 1        | vf-syt    | 0 0 1 1                             | 0 1 1 1         | -b-f-syt   | 0 1 0 1                | 0 1 1 1 |

| Tf,Bc      | 0 0 0 1                                          | 1 0 0 0        | Iv,Tf,Bc  | 0 0 1 1                             | 1 0 0 0         | Be,Tf,Bc   | 0 1 0 1                | 1 0 0 0 |

| Tf,Bc,Te   | 0001                                             | 1 0 0 1        | IvTfBcTe  | 0 0 1 1                             | 1 0 0 1         | BeTfBcTe   | 0 1 0 1                | 1 0 0 1 |

| Tf,Bc,Bd   | 0001                                             | 1 0 1 0        | IvTfBcBd  | 0011                                | 1 0 1 0         | BeTfBcBd   | 0101                   | 1 0 1 0 |

| TfBcBdTe   | 0001                                             | 1 0 1 1        | vfc-yt    | 0 0 1 1                             | 1 0 1 1         | -b-fc-yt   | 0 1 0 1                | 1 0 1 1 |

| Tf,Bc,S1   | 0001                                             | 1 1 0 0        | IvTfBcS1  | 0 0 1 1                             | 1 1 0 0         | BeTfBcS1   | 0 1 0 1                | 1 1 0 0 |

| TfBcS1Te   | 0001                                             | 1 1 0 1        | vfcs-t    | 0 0 1 1                             | 1 1 0 1         | -b-fcs-t   | 0 1 0 1                | 1 1 0 1 |

| TfBcS1Bd   | 0 0 0 1                                          | 1 1 1 0        | vfcsy-    | 0 0 1 1                             | 1 1 1 0         | -b-fcsy-   | 0 1 0 1                | 1 1 1 0 |

| fcsyt      | 0001                                             | 1 1 1 1        | vfcsyt    | 0 0 1 1                             | 1 1 1 1         | -b-fcsyt   | 0 1 0 1                | 1 1 1 1 |

(Cont.)

Table 3-6 (Cont.)

FB+\_Stat Symbol Table Definitions

|            | ST Group Value         |          | ST Group Value         |          | ST Group Value                      |

|------------|------------------------|----------|------------------------|----------|-------------------------------------|

|            | ST_7 ST_3<br>ST_6 ST_2 |          | ST_7 ST_3<br>ST_6 ST_2 |          | ST_7 ST_3<br>ST_6 ST_2              |

| Symbol     | ST_5 ST_1<br>ST_4 ST_0 | Symbol   | ST_6                   | Symbol   | ST_6 ST_2<br>ST_5 ST_1<br>ST_4 ST_0 |

| Be, Iv     | 0 1 1 0 0 0 0 0        | Wt       | 1 0 0 0 0 0 0 0        | Wt,Iv    | 1 0 1 0 0 0 0 0                     |

| Be, Iv, Te | 0110 0000              | Wt,Te    | 1000 0000              | Wt,Iv,Te | 1010 0000                           |

| Be, Iv, Bd | 0110 0010              | Wt,Bs/Ed | 1000 0010              | Wt,Iv,Bd | 1010 0010                           |

| BeIvBdTe   | 0110 0010              | Wt,Bd,Te | 1000 0010              | WtIvBdTe | 1010 0010                           |

| Be, Iv, Sl | 0110 0110              | Wt,S1    | 1000 011               | Wt,Iv,Sl | 1010 0111                           |

| BeIvSlTe   | 0110 0101              | Wt,S1,Te | 1000 0100              | WtIvSlTe | 1010 0100                           |

| BeIvS1Bd   | 0110 0101              | Wt,S1,TC | 1000 0101              | WtIvS1Bd | 1010 0101                           |

| -bvsyt     | 0110 0110              | WtS1BdTe | 1000 0110              | w-vsyt   | 1010 0111                           |

| Be, Iv, Bc | 0 1 1 0 0 1 1 1        | Wt,Bc    | 1000 1000              | Wt,Iv,Bc | 1010 1000                           |

| BeIvBcTe   | 0110 1000              | Wt,Bc,Te | 1000 1000              | WtIvBcTe | 1010 1000                           |

| BeIvBcBd   | 0110 1010              | Wt,Bc,Tc | 1000 1001              | WtIvBcBd | 1010 1010                           |

| -bv-c-yt   | 0110 1010              | WtBcBdTe | 1000 1010              | w-v-c-yt | 1010 1010                           |

| BeIvBcS1   | 0110 1100              | Wt,Bc,S1 | 1000 1011              | WtIvBcS1 | 1010 1011                           |

| -bv-cs-t   | 0110 1101              | WtBcSlTe | 1000 1101              | w-v-cs-t | 1010 1101                           |

| -bv-csy-   | 0110 1110              | WtBcS1Bd | 1000 1110              | w-v-csy- | 1010 1110                           |

| -bv-csyt   | 0110 1111              | wcsyt    | 1000 1111              | w-v-csyt | 1010 1111                           |

| Be, Iv, Tf | 0 1 1 1 0 0 0 0        | Wt,Tf    | 1001 0000              | Wt,Iv,Tf | 1011 0000                           |

| BeIvTfTe   | 0 1 1 1 0 0 0 1        | Wt,Tf,Te | 1001 0001              | WtIvTfTe | 1011 0001                           |

| BeIvTfBd   | 0 1 1 1 0 0 1 0        | Wt,Tf,Bd | 1001 0010              | WtIvTfBd | 1011 0010                           |

| -bvfyt     | 0 1 1 1 0 0 1 1        | WtTfBdTe | 1001 0011              | w-vfyt   | 1011 0011                           |

| BeIvTfS1   | 0111 0100              | Wt,Tf,sl | 1001 0100              | WtIvTfS1 | 1011 0100                           |

| -bvf-s-t   | 0111 0101              | WtTfS1Te | 1001 0101              | w-vf-s-t | 1011 0101                           |

| -bvf-sy-   | 0111 0110              | WtTfS1Bd | 1001 0110              | w-vf-sy- | 1011 0110                           |